Корпорация Toshiba объявила на прошлой неделе о разработке энергоэффективной многоядерной системы на чипе (SoC) для встраиваемых компьютерных систем, которые будут применяться, в частности, в автомобильной отрасли и в цифровых устройствах. Имеющийся на настоящий момент прототип содержит 64 вычислительных ядра, что в восемь раз больше по сравнению с чипом предыдущего поколения, и предлагает в 14 раз большую производительность.

Современные тенденции в развитии мультимедийных устройств, в частности, в плане кодирования и декодирования видео и технологий лицевого распознавания, требуют многоядерных процессоров, сочетающих высокую производительность при низком энергопотреблении. Инженеры Toshiba уверяют, что смогли добиться именно такого сочетания на уровне, приемлемом для встраиваемых систем.

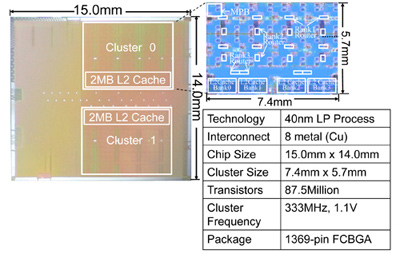

Площадь чипа составляет без малого 210 кв. мм и состоит он из двух 32-ядерных кластеров с динамически настраиваемыми вычислительными ядрами, аппаратных ускорителей, 2-канального контроллера памяти DDR3 и других периферийных компонентов. Ядра в каждом кластере делят между собой общую кеш-память второго уровня объёмом 2 Мб. Масштабируемость и низкое энергопотребление обеспечиваются высоким уровнем параллельных вычислений в мультимедийных приложениях. Так, для декодирования видео формата MPEG4-AVC/H.264 в качестве 1080р с частотой 30 кадров в секунду требуется всего 500 мВт, а для обработки изображения с разрешением 4K2K с частотой 15 кадров в секунду всего 800 МВт. За распознавание изображений здесь отвечают встроенные аппаратные ускорители. Разработчики обещают уровень производительности новой системы на чипе до 1,5 триллиона операций в секунду на частоте 333 МГц.

Энергоэффективность чипа заложена на уровне его физической структуры благодаря применению ряда технологий, таких как многоуровневая система управления энергопотреблением различных компонентов чипа и их тактовой частотой и собственной технологии Toshiba для кодирования данных с применением триггерных цепей. Также даёт о себе знать и переход с 65 нм на 40 нм технологический процесс.